Circuits & Devices Chapter

Chair:

Vice Chairs:

Email:

jiupeng.zhang@mail.utoronto.ca

dhruvnp@yorku.ca

Past Events

2026

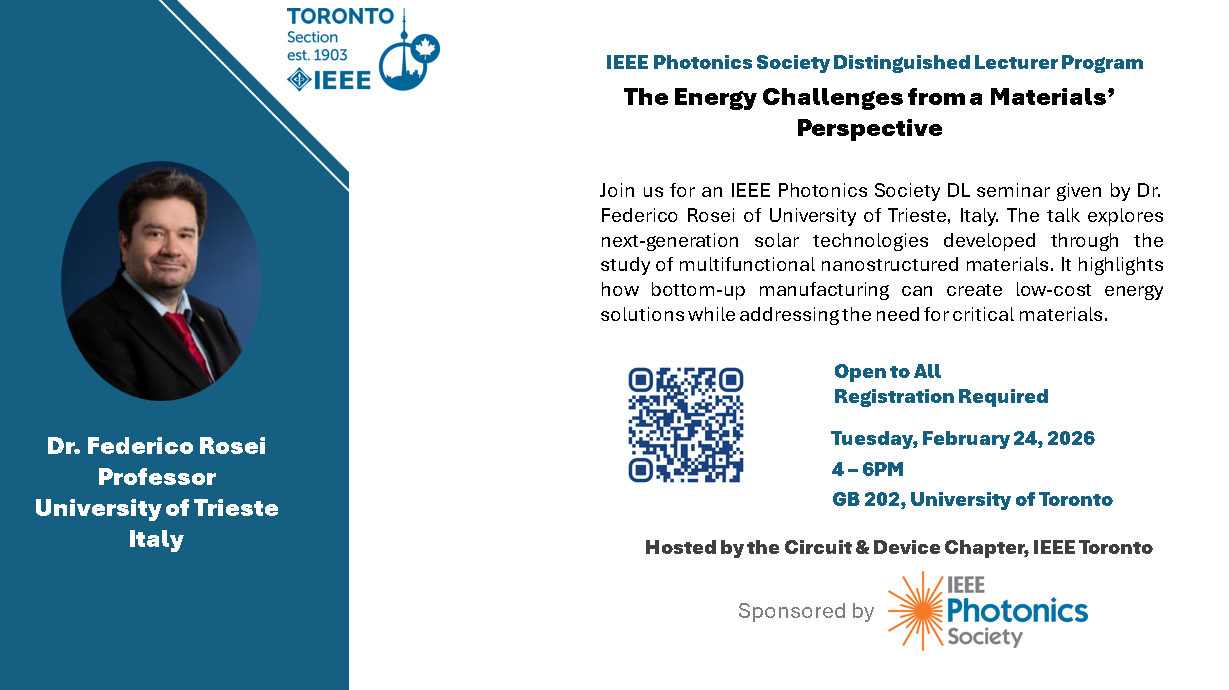

(February 24) The Energy Challenges from a Materials’ Perspective

The quest for sustainable development dictates an urgent transition from fossil fuels to renewables. This presentation focuses on next generation (solar) energy technologies from a materials perspective. We study structure property/relationships in advanced materials, emphasizing multifunctional systems that exhibit several functionalities. Such systems are then used as building blocks for the fabrication of various emerging technologies. In particular, nanostructured materials synthesized via the bottom–up approach present an opportunity for future generation low cost and low energy intensive manufacturing of devices. We focus on recent developments in solar technologies, including third generation photovoltaics, solar hydrogen production, luminescent solar concentrators and other optoelectronic devices, highlighting the role and importance of critical raw materials.

Speaker: Professor. Federico Rosei, University of Trieste

View the gallery:

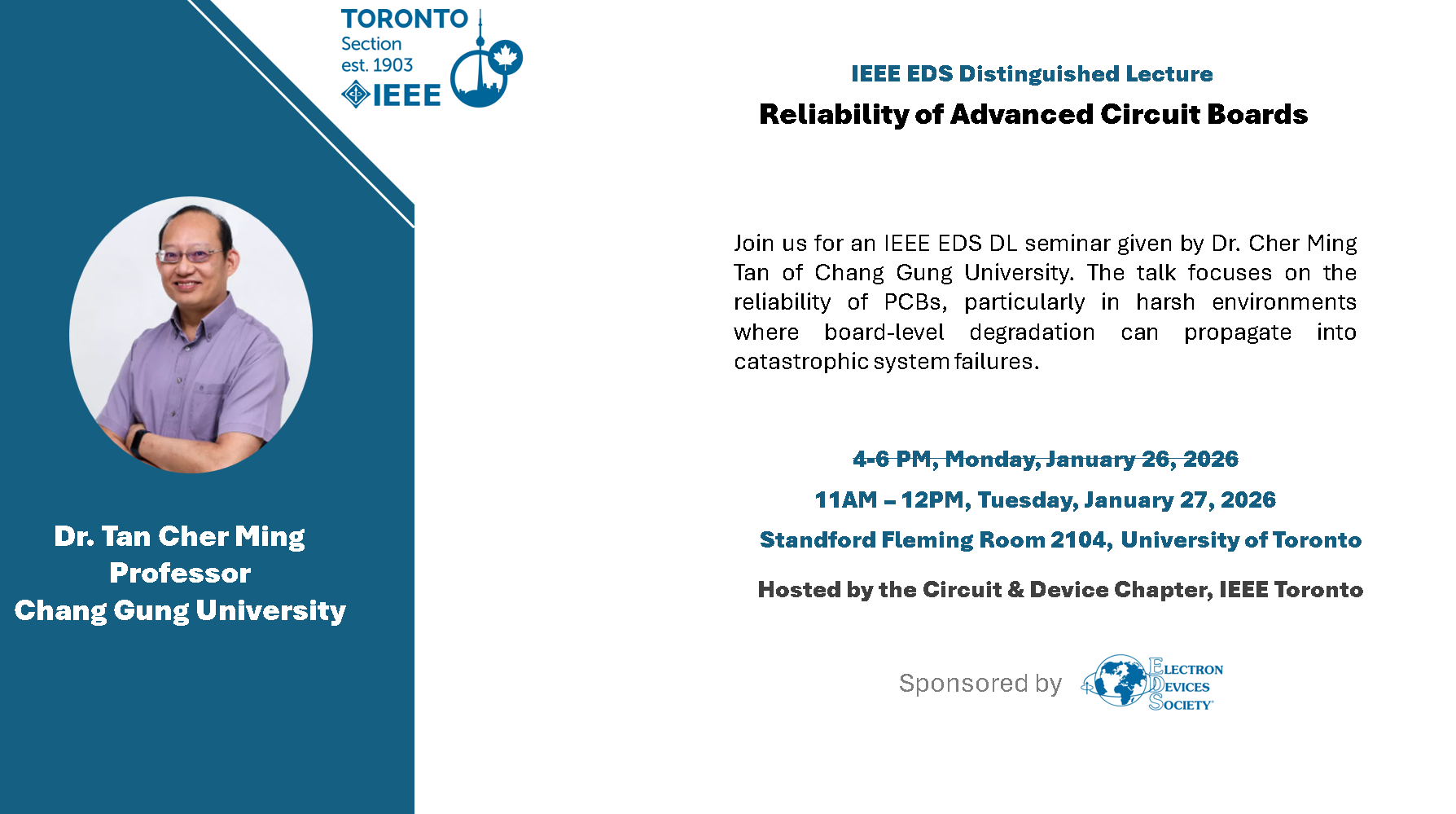

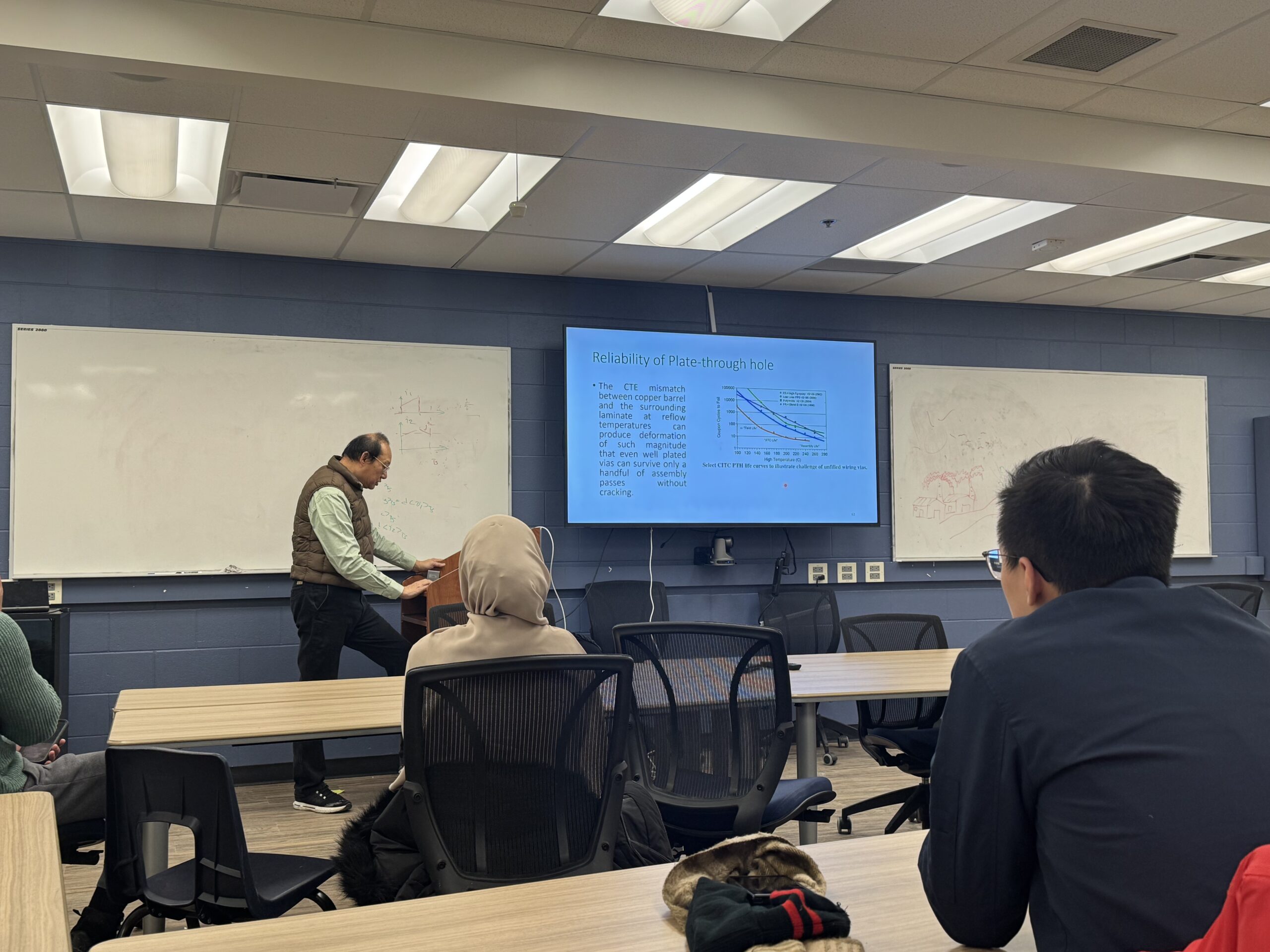

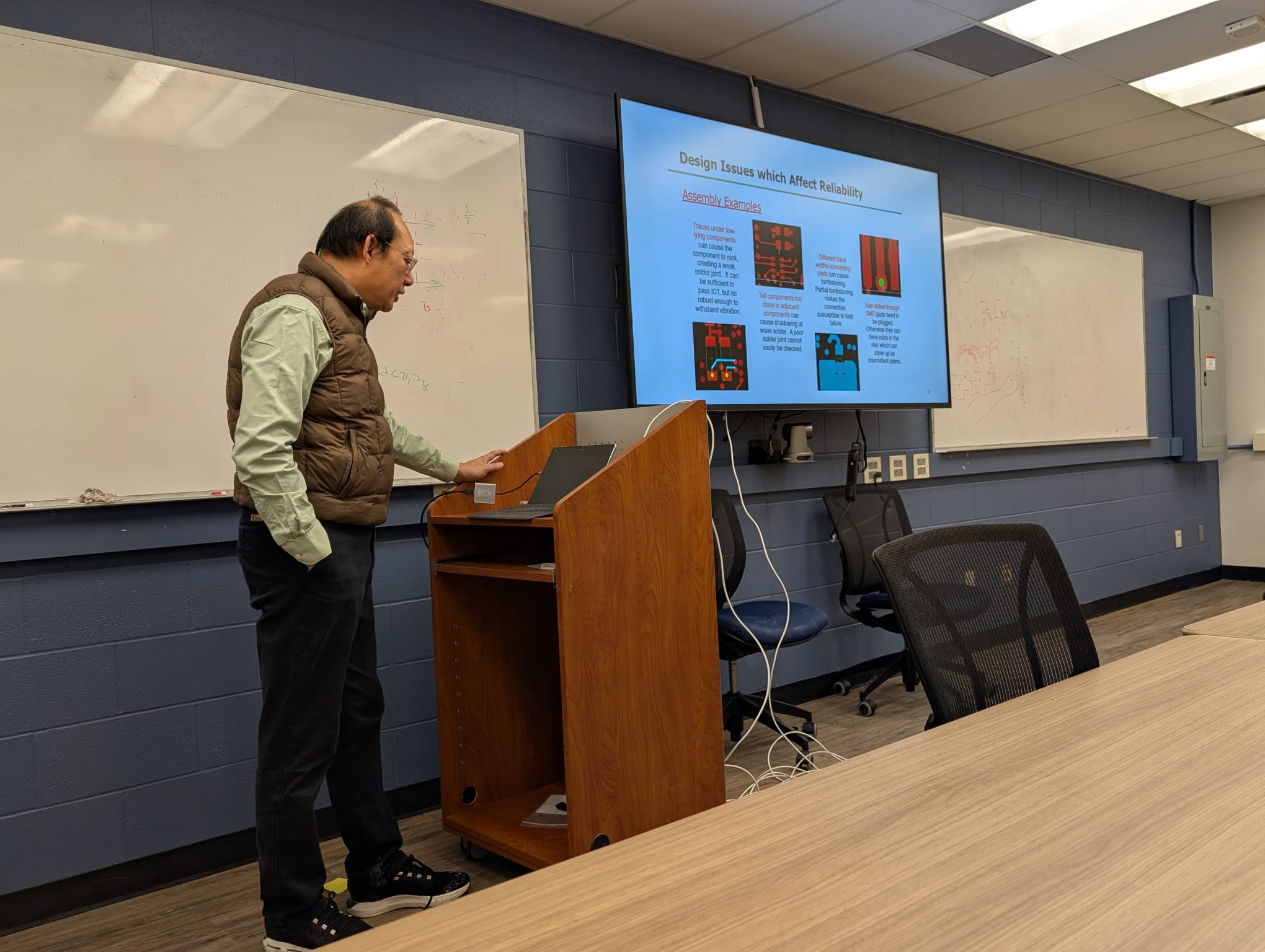

(January 27) Reliability of Advanced Circuit Boards

Description:

Printed circuit boards (PCBs) are fundamental to all electronic systems, providing component integration, electrical interconnection, mechanical support, and

thermal management. Despite their critical role, PCB reliability has historically received far less attention than that of electronic components, particularly active devices. This gap is partly due to the perception of PCBs as mature, supporting structures rather than primary reliability drivers.

However, PCB technologies continue to evolve, especially for mission‑critical applications operating under high temperature, high humidity, or radiation‑intensive environments. In these conditions, PCB failure mechanisms can significantly influence overall system reliability, yet published studies remain limited.

This talk will present key PCB failure mechanisms and highlight how PCB‑level degradation can propagate to system‑level failures, drawing on insights from my recent research. The goal is to encourage engineers to treat PCBs as integral elements of system reliability analysis, particularly in high‑reliability and safety‑critical applications.

Speaker: Professor. Tan Cher Ming, Chang Gung University

The link to the slide deck https://www.ieeetoronto.ca/wp-content/uploads/2026/01/DL-talk-note.pdf

View the gallery:

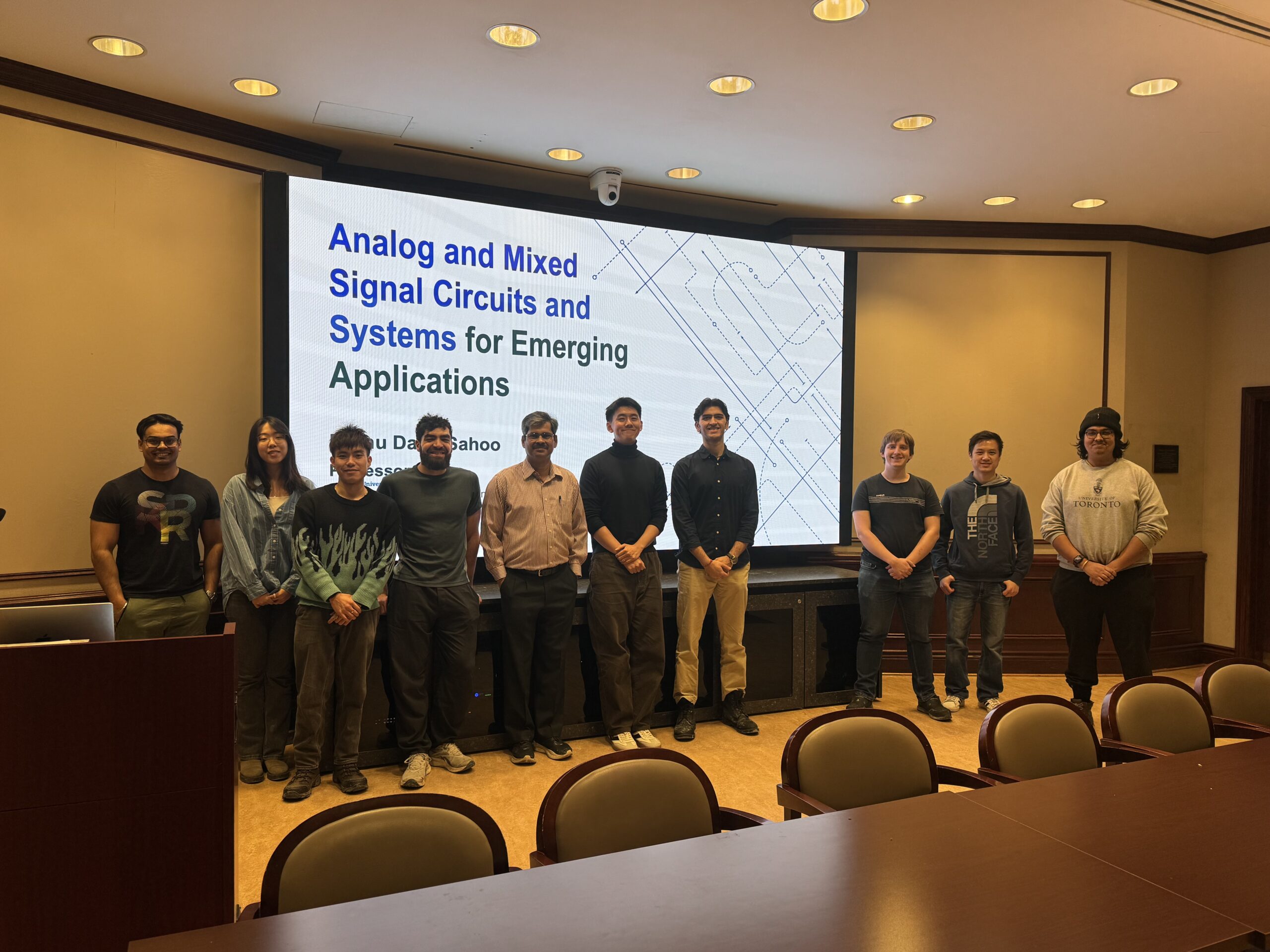

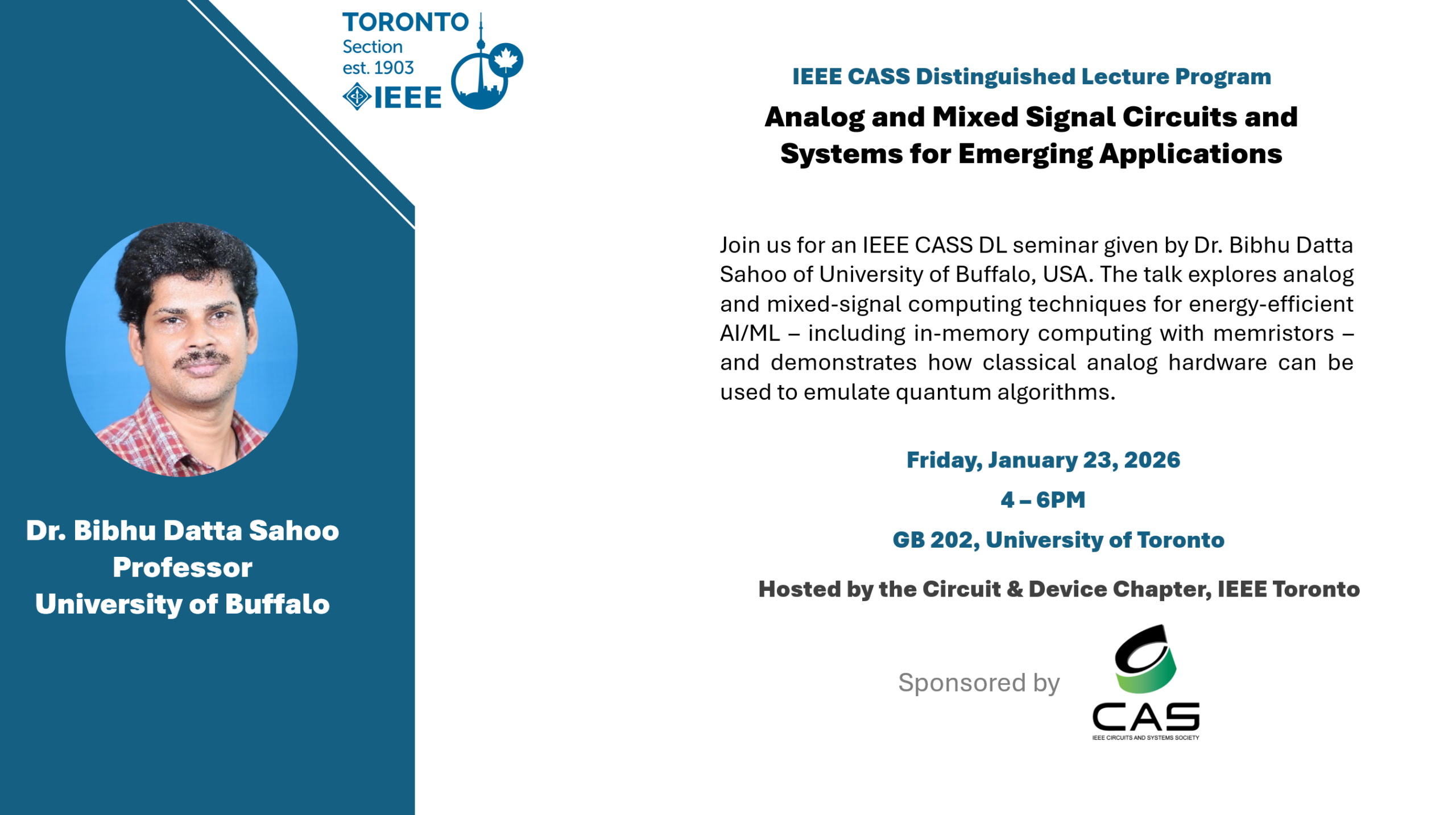

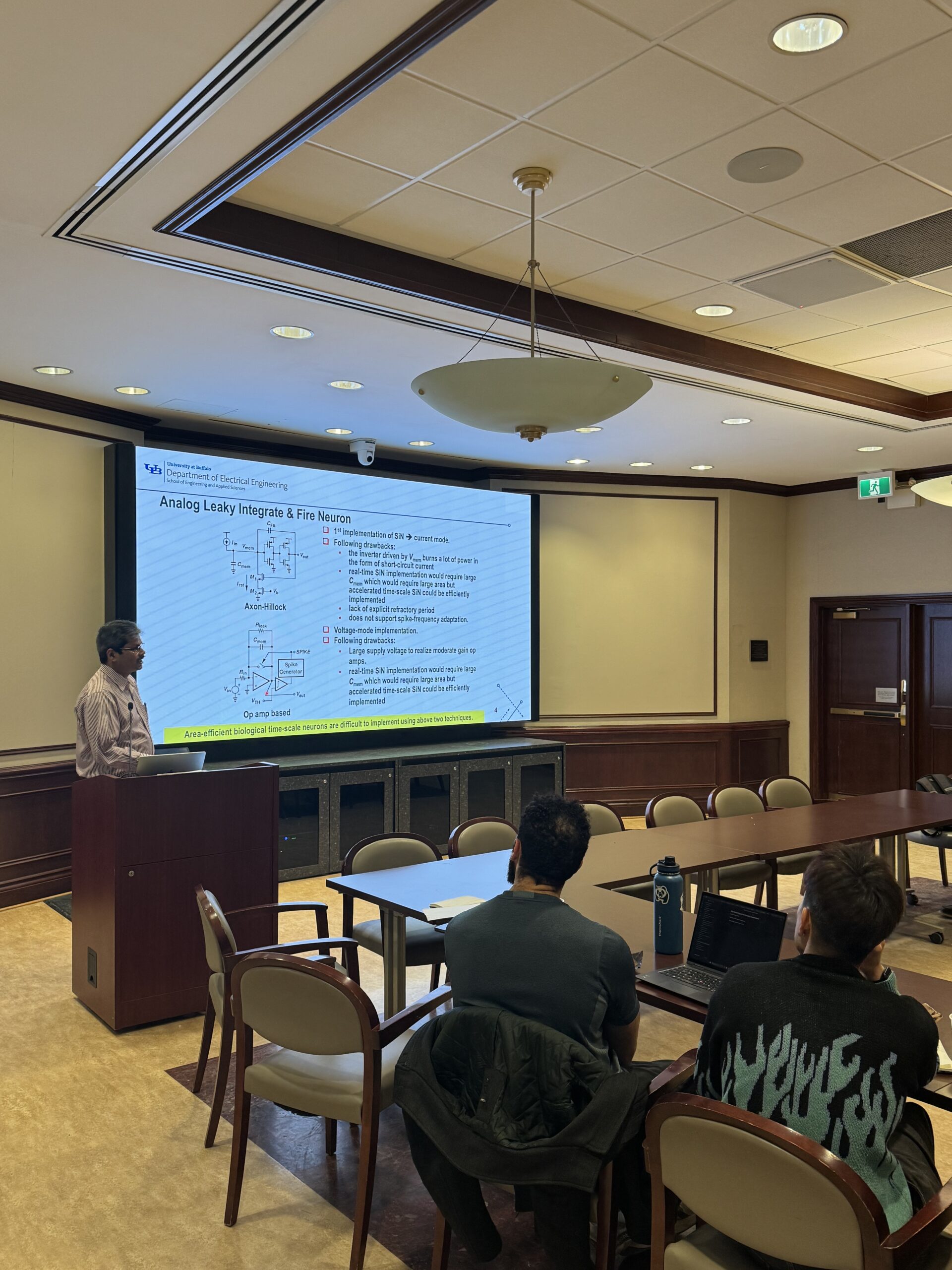

(January 23) Analog and Mixed Signal Circuits and Systems in Emerging Applications

Description:

Quantum Computing, having the ability to exponentially enhance the raw computing power, and Artificial Intelligence (AI), having the ability to impart unprecedented intelligence to connected devices through algorithms that learn, are the two key technologies of the 21st century. Although novel devices can significantly advance the field of quantum computing, conventional CMOS based analog and mixed signal circuits can enable quantum computing using classical op amp based circuits. AI algorithms on the other hand are tolerant to errors in computation, thereby enabling approximate and low-precision computing which has resulted in the resurrection of more than half-a-century old analog computing.

This talk would present various analog computing techniques that could enable AI algorithms or more specifically machine learning (ML) algorithms. The talk could also delve into mixed-sginal computing where it will dive into the details of in-memory computing as well as adoption of novel memory devices, viz., memristors, to enable energy efficient computing. The talk would also present some classical analog hardware for emulating quantum algorithms, like Grover’s search algorithm, for quantum computing systems.

Speaker: Professor. Bibhu Datta Sahoo, University of Buffalo

View the gallery:

2025

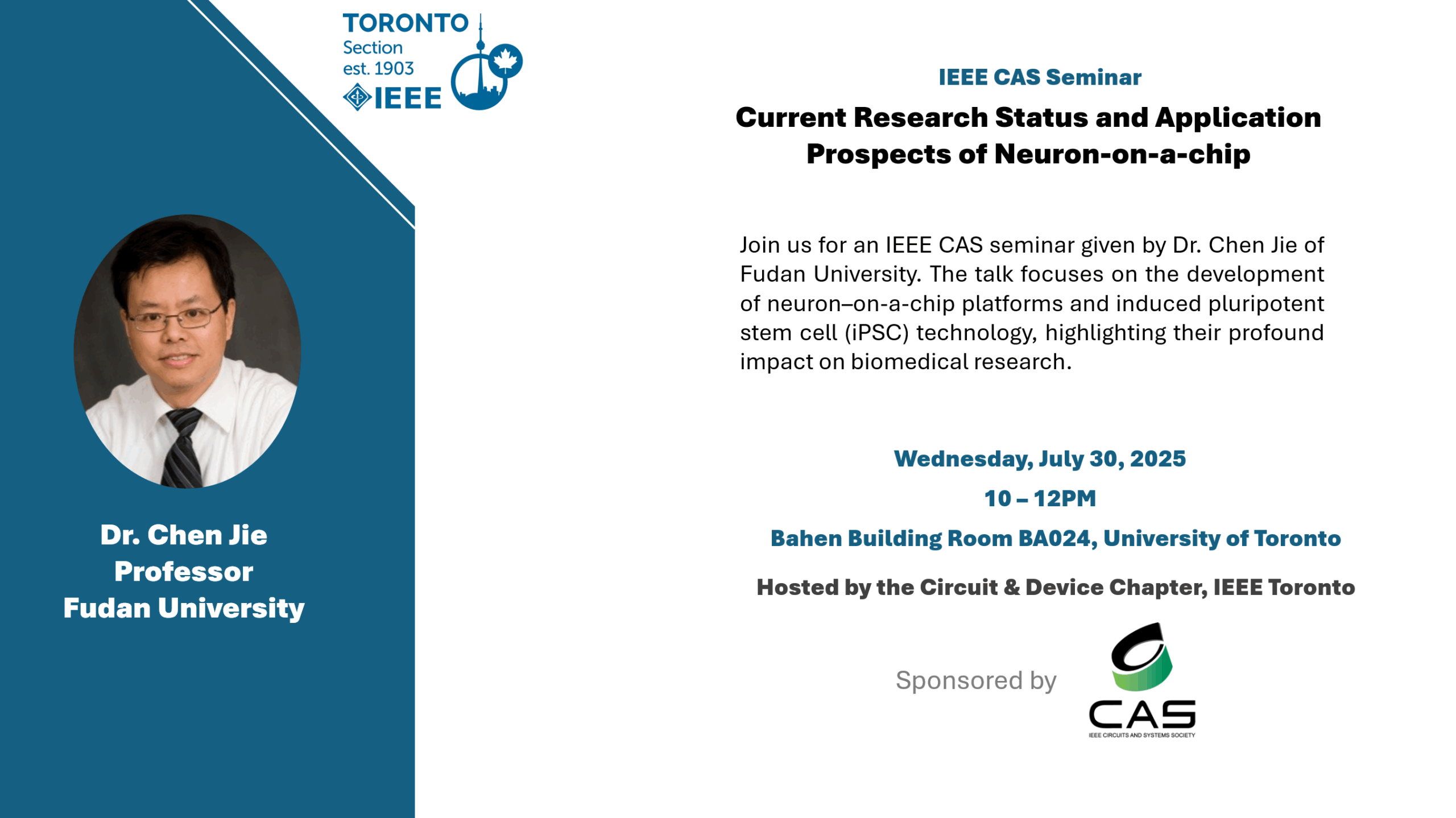

(July 30) Current Research Status and Application Prospects of Neuron-on-a-chip

With the advancement of microfluidic and organoid technologies, neuron-on-a-chip platforms have demonstrated tremendous potential in precisely replicating the three-dimensional structure of the brain, simulating intercellular interactions, and reconstructing in vitro physiological models. On one hand, compared to traditional two-dimensional cell cultures, neuron-on-a-chip systems can not only construct more complex physiological architectures but also provide a dynamically controllable developmental environment for neural tissues. On the other hand, compared to animal models, brain-on-a-chip technology not only effectively addresses the limitations in the number of available animal models, but also alleviates, to some extent, the ethical concerns associated with animal experiments. Through induced pluripotent stem cell (iPSC) technology, we can directly model human brain pathological phenotypes on chips, overcoming challenges posed by interspecies differences in animal models, and enabling the investigation of key events in the progression of human neurological disorders. In addition, neuron-on-a-chip systems can be integrated with other organoid tissues on microfluidic chips to create multi-organ-on-a-chip platforms. Compared to single-organ chips, multi-organ systems can reconstruct multiple human tissue organoids in vitro, enabling precise simulation of inter-organ interactions.

Speaker: Chen Jie, Fudan University, IEEE Fellow

View the gallery:

2024

The IEEE Photonics Society / Standards Committee recently published a whitepaper on Fiber Attach. Transmission of light between or in and out of any photonic platform normally requires attachment to a fiber that is used as a flexible optical waveguide. An effective fiber attach involves many requirements and metrics that have so far involved decades of research. The presentation will cover the whitepaper in detail, some technical background, the path forward, and how to become involved.

Speaker: John S. Mazurowski of Penn State Applied Research Laboratory

View the poster:

Silicon Valley is commonly acknowledged as the tech capital of the world. How did Silicon Valley come into being, and what can we learn? The story goes back to local Hams trying to break RCA’s tube patents, Stanford “angel” investors, the sinking of the Titanic, WW II and radar, and the SF Bay Area infrastructure that developed – these factors pretty much determined that the semiconductor and IC industries would be located in the Santa Clara Valley, and that the Valley would remain the world’s innovation center as new technologies emerge, and be the model for innovation worldwide.

This talk will give an exciting and colorful history of development and innovation that began in Palo Alto in 1909. You’ll meet some of the colorful characters – Cyril Elwell, Lee De Forest, Bill Eitel, Charles Litton, Fred Terman, David Packard, Bill Hewlett, Bill Shockley and others – who came to define our worldwide electronics industries through their inventions and process development. You’ll understand some of the novel management approaches that have become the hallmarks of its tech startups. Many of these attributes can be found in other technology hubs; however, the SF Bay Area has five generations of experience, as well as a “critical mass” of talent, making it difficult for others to catch up. In this talk, the key attributes will be illustrated and analyzed, for consideration by other tech hubs, and for entrepreneurs interested in creating their own start-ups or understanding them.

Speaker: Paul Wesling, IEEE Fellow

Link to video recording: https://ieeetv.

Link to slides: https://pwesling.com/

View the gallery:

2023

Noise-Shaping (NS) SAR ADCs become popular recently thanks to their low-power and high-resolution features. This presentation first summarizes and benchmarks different discrete-time (DT) NS-SAR implementations in literature. An open-loop duty-cycled residue amplifier is selected as a power-efficient solution to realize high residue gain. Then, a digital-predicted mismatch error shaping technique is introduced to improve the DAC linearity. The proposed DT NS-SAR ADC achieves 80 dB SNDR, 98 dB SFDR in a 31.25 kHz bandwidth while consuming 7.3 μW. Next, the NS-SAR architecture is extended from DT operation to continuous-time (CT) operation. The ADC sampling switch is removed and the loop filter is duty cycled to realize the CT NS-SAR operation. Compared to DT designs, the CT NS-SAR ADC is easy to drive and has inherent anti-aliasing function. As a proof of concept, the proposed CT NS-SAR ADC achieves 77 dB SNDR, 86 dB SFDR a 62.5 kHz bandwidth with a power consumption of 13.5 μW.

Speaker: Professor Pieter Harpe of Eindhoven University of Technology

Link to the pdf: noise-shaping-SAR-ADCS-event-poster.pdf

2022

Power has become the key driving force in processor as well AI specific accelerator designs as the frequency scale-up is reaching saturation. In order to achieve low power system, circuit and technology co-design is essential. This talk focuses on related technology and important circuit techniques for nanoscale VLSI circuits… (Read more)

Video recording of this talk can be made available to attendees of the event. If you would like to request access to this file please send an email to wagih.ismail@ieee.org.

View the poster:

Since late 2000’s, SAR ADCs have become one of the most popular ADC architectures showing not only excellent energy efficiency but also competitive conversion speed owing to the digital-friendly compact structure and architectural evolution in deep submicron technologies… (Read more)

This event features representatives from prominent companies with offices in the GTA to give talks on active areas of innovation in the circuits & electronics industry. These sessions will help familiarize students with where companies are most actively focussing innovation efforts… (Read more)

View the gallery: